Do We Need a New Hardware Description Language? [Hackaday]

When you think about hardware description languages, you probably think of Verilog or VHDL. There are others, of course, but those are the two elephants in the room. Do we need another one? [Veryl-lang] thinks so. The Veryl language is sort of Verilog meets Rust. What makes Veryl interesting is that it transpiles to normal SystemVerilog, so it will — probably — work with your existing tool chains.

That means you can define your logic Veryl, have it output SystemVerilog, and then use that Verilog in your vendor’s (or an open source) Verilog tool. The output is supposed to be human-readable Verilog, too, so you don’t have to transport opaque blocks of gibberish.

You can find an example of the language on GitHub in the documentation. If you can read any HDL, you won’t find it very different. That might be the weakest part — from a user’s point of view, this might just as well be Verilog. The documentation claims that parsing the language is easier, but if you are just going to convert it to Verilog anyway, it might be as well to just write to Verilog. Then again, we know Verilog well enough that we are probably biased.

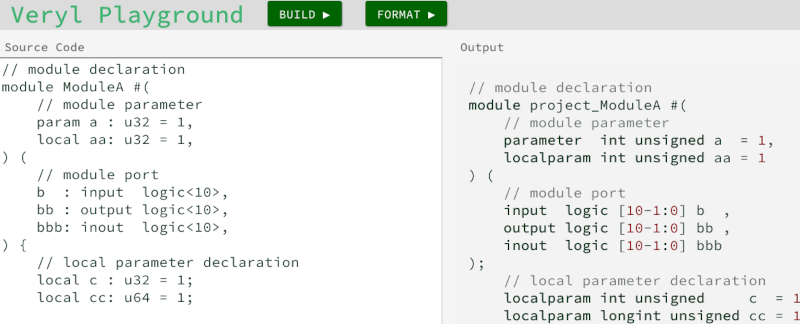

If you want to try it easily, there’s a browser-based “playground” to try. For example, the input:

// module declaration

module Hackaday (

// module port

v : input logic<32>,

q : output logic<32>

) {

assign q=~v;

}

Resulted in:

// module declaration module project_Hackaday ( // module port input logic [32-1:0] v, output logic [32-1:0] q ); assign q = ~v; endmodule

Perhaps a little nicer, but not an overwhelming improvement.

What do you think? Will you try Veryl? Let us know in the comments. It isn’t the only alterative choice, of course. There’s SpinalHDL and MyHDL, to name two.

![do-we-need-a-new-hardware-description-language?-[hackaday]](https://i0.wp.com/upmytech.com/wp-content/uploads/2024/03/173787-do-we-need-a-new-hardware-description-language-hackaday.png?resize=800%2C324&ssl=1)